- Asynchronous Reclocking

- I2S

- Output Stage

- Error Correction vs. Jitter

- Slaving Computer Soundcards

- Battery for Digital Schematics?

- Stacking Multiple Converter Chips

- Benchmark's UltraLock

- Digital Filtering

- One-box CD Players

- Synchronous Reclocking

- Jitter Sources

- Large Buffer

- Disbelief in LessLoss

- A/D Converters

- Sampling Rates

Question:

Unfortunately, the explanations on your web site don't make any sense to me. Granted I'm not a signals engineer - but to be realistic, if you are going to sell me your product based on its technical merits, I need to be able to understand them. Could you explain exactly why this statement is true? "When the Jittered audio signal arrives at the DAC, it is quantized into place temporally and is then played, in perfect synch with the clock oscillator, which is right next to it." I understand that you are sending the master clock signal from the DAC 2004 out to the transport via a cable. This cable, being a real-world devices and not a perfect signal transmitter, will introduce some jitter into the signal, no?

LessLoss Reply:

Absolutely correct. Our clock signal is largely jitter-free (on the order of only 10 ps perhaps). But yes, you are correct. Any cable will introduce jitter into the signal, and the longer the cable, the more jitter there will be.

Then a second cable sends the digital output of the CD player back to the DAC. Won't this cable introduce yet more jitter?

LessLoss Reply:

Yes, again, you are absolutely correct. The second cable carrying the SPDIF signal from the CD player is quite jittery.

Do they cancel each other out somehow?

LessLoss Reply:

Yes. The explanation is on this page. We invite you to read that page carefully. Our solution is Setup #4 (Digital Master Mode, 8x Oversampling, Single-stage Synchronous Reclocking). In the picture depicted on the webpage mentioned above, you can see schematically that the oscillator, largely jitter-free, is located right next to the Oversampling chip, and is located in the DAC enclosure itself. The fact that the Oversampling chip is being timed by the very same Master Clock that the rest of the system is running off of means that when the jittery SPDIF signal arrives at the Oversampling chip, its now (very) jittery clock signal is in effect "thrown away" and replaced by the new, non-jittery original clock signal! Do you see now that this is a totally synchronous process?

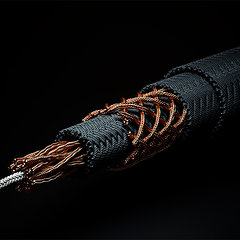

Not to add to your confusion, but to be complete, I must simply let you know that there is more electrotechnically involved than meets the eye, but in general the concept as stated above is correct. We know that even in this setup, some amount of jitter can still come through, and that is why we go to such great lengths regarding the hyper-shielding of the digital lines. Also, provision of additional synchronous reclocking at other stages of the digital signal also help, but this is not the main issue. The method as described above (synchronous reclocking) is the best possible method of reducing jitter and minimizing the effects of distance the digital signals have travelled.

Not only distance adds jitter to the digital signals. The turning CD and laser mechanism also adds an amount of jitter.

Beware of Fakes

Beware of Fakes